글쓴이 : SOONDORI

직전 글에 이어지는 내용으로서, 기기 관찰 중 목격되었던 특이 반응을 정리한다.

* 관련 글 : 일본 내수용 SONY ST-V5 튜너와 디지털 제어 시스템 (5)

■ 수신 범위 설정

PLL IC #5핀 즉, 마이크로 컨트롤러 동작용 클럭을 공급하는 라인에 오실로스코프 프로브를 접촉하면 클럭 오류가 발생한다. 전원 버튼을 눌러 리부팅하면 VFD는 0.0Mhz~199.9Mhz를 순환 지시하고. 태연히, 아주 자연스럽게…

그것은 1) 0.0Mhz~199.9Mhz의 절대폭 200Mhz라는, 하드웨어적으로 고정된 기본 Span이 있다는 것이고, 2) 그 대신 국가/지역별 선국 시작점과 끝점 즉, 76Mhz~90Mhz 또는 88Mhz~108Mhz의 선택은 프로그램 변수로 지정된다는 뜻이다. 거꾸로 해석하면 컨트롤러에 기록된 프로그램에서 특정 코드 한 두 줄을 바꾸면 우격다짐으로 국내 대응이 가능하다는 이야기.

추정하건대 A=1234, B=6789와 같은… 여기서 1234, 6789는 88,000,000hz와 같은 목표 주파수가 아니라 PLL IC/Phase Detection 블럭의 <목표 클럭 대 프론트엔드 피드백 클럭의 오차> 검출용 상수(= 아래 PLL 내부 피드백 분주비율)

* 관련 글 : 디지털 튜너의 서보-락, 쿼츠-락 그리고 PLL

안타깝게도 One Time 기록형 마이크로 컨트롤러인지라… 1) 북미향 마이크로 컨트롤러로 대체하거나, 2) 8비트 이상의 모던한 마이크로 컨트롤러 + 그에 걸맞은 프로그램 조합으로 대체하지 않는 이상, 물리적 수정은 어렵다. 물론 두 가지 모두… 하자고 하면 할 수 있는, 충분히 현실성 있는 대안.

■ PLL 제어 최대치

Dial Span을 200Mhz로 강제 설정하고 관찰해보면,

○ PLL IC #11 클럭은… 76~90Mhz 상태에서 최소 65.275Mhz(=76Mhz), 최대 79.275Mhz(=90Mhz)이었다. 강제 설정 후에는 VFD 199.9.0Mhz에서 주파수 카운터가 81.230Mhz 제시한다. 190.0Mhz에서 76.874Mhz, 176.0Mhz에서 62.8749Mhz, 188.0Mhz에서 74.87488Mhz…

대략 피드백 펄스 81.230Mhz까지는 마이크로 컨트로러와 프론트엔드 Varactor가 기대한 대로 반응하는 상황. 계산해보면 최대 수신 주파수는 VFD 91.955Mhz@PLL 81.230Mhz. 약 2Mhz UP! 최소는 VFD 11Mhz@PLL 59.893Mhz.

버랙터 동작(전압-커패시턴스)에 일정 부분 여유가 있으니 일본 내수용 조건에서조차 약간의 주파수 확장 여지가 있는 것. (대부분의 경우에도 그러할 듯하다) 물론 제대로 확장하려면 프론트엔드에 사용된 Varactor 데이터 시트/전압-커패시턴스 그래프와 코일값을 참조하여 LC 조합을 적당히 변경해야 한다.

* 관련 글 : Toshiba TC-9147BP, 디지털 튜너 컨트롤러

○ 데이터 시트에 명시된 FM 모드 통제 전압은 2.8V에서 20V까지. 현물은 3.2~21.7V. 추정하건대 VFD 91.955Mhz@PLL 81.230Mhz 확장 사례에서 통제 전압은 전원 라인 전압 이하 조건으로, 약간 증가되었을 것이다. 뭐… 쥐어짜기를 한 것.

■ PLL IC 파형

아래는 70~90Mhz 동작 상태에서 캡처한 내용.

○ #9핀, Shift Resistor SHIFT CLOCK : 기준 펄스의 분주를 정의하는 16비트 BCD 코드 = 4비트 × 4개에 상당히는 파형. (오실로스코프 파형만으로는 구체적인 비트열을 파악하기 어렵다)

○ #8핀, Shift Resistor DATA-IN : BCD 코드

○ #7핀, Programmable Counter LATCH : 데이터 펄스 인식의 기준점을 제공하는 단발성 펄스

○ #5, Standard Counter OUT : 마이크로 컨트롤러 구동용으로 쓰이는 360Khz 연속 펄스.

○ #11핀, Phase Detector OUT

출력 펄스는 다음 단 적산기에서 프론트 엔드용 통제 전압으로 변환될 것이다.

1) PWM 제어/Duty 제어에서 사용되는 On Time 변화라면… 통전 간격이 넓으면 높은 전압, 좁으면 낮은 전압. 높으면 C가 작아지고 낮으면 커진다. 그에 따라 선국 주파수는 낮아지고 높아지고.

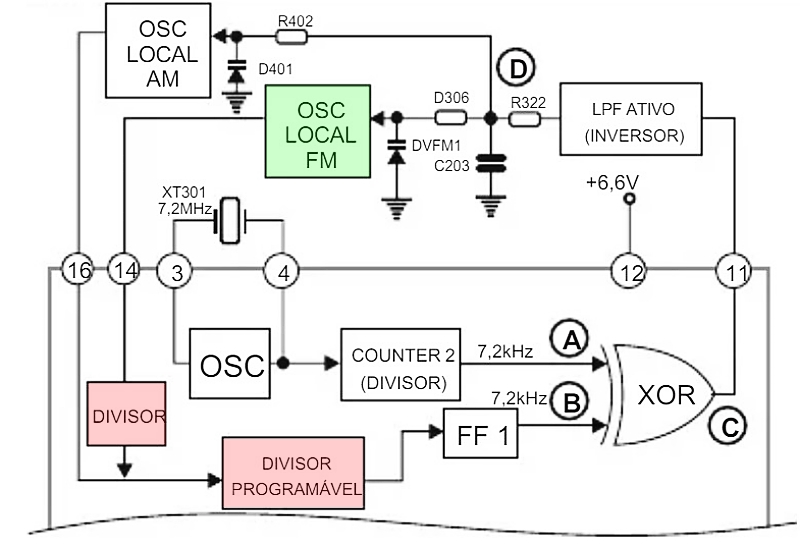

2) 단순히 고정된 펄스의 이격 주기 즉, 간격을 조정하는 방식이라면… 역시 전압, C값의 변화는 같은 논리로. 오실로스코프로는 판별이 어려운데 PWM 제어는 구식 PLL IC에 너무 과한 듯하니 아무래도 후자에 한 표를 던지고… (내용 수정, 2021.11.04) XOR 등 게이트로 연산하면 두 클럭의 타이밍 차이를 쉽게 펄스폭으로 변환할 수 있을 것. 이번에는 가변 폭 방식에 한 표를.

디지털이 아날로그와 만나는 이 포인트의 처리를 개념화하자면, 통제 전압 = Fx(펄스 간격, Loop Filter 함수(On-Time 폭), 적산기 시정수, 기타).

(▲ 실제 파형은 단순하고 깨끗하게 잡히지 않음. 작은 단발성 피크가 보이고 어찌보면 가변폭 펄스처럼 보이기도 하고…)

아무튼… PLL IC와 4비트 마이크로 컨트롤러가 묶인 구식 제어는 모던한 8비트 이상 마이크로 컨트롤러 하나로 완전히 대체될 수 있다고 본다.

(▲▼ 내용 추가. PLL IC 출력인 디지털 펄스를 아날로그 DC 전압으로 만들기 위해 위 C403, C404 커패시터 활용 Charging Pump 즉, 적산기 개념이 적용되었고… Peak성 노이즈 펄스를 제거하기 위해서 Active Low Pass Filter를 구성하되 PLL 폐(廢)루프에 사용되었으므로 ‘Loop’를 강조하여 PLL Loop Filter라고 한다. 출처 : TI사 기술정보-Fractional-Integer-N PLL Basics)

이상과 같이, 소니 ST-V5 튜너의 PLL 선국 제어는 ‘디지털의 틀’ 안에서 처리되고 있다. 그러니까… 숫자가 표시되어 디지털이 아니라 그 안에 디지털 제어가 들어있으니까 Digial.

다음은 현상 유지 조건의 마지막 수정 대안으로서, 마이크로 컨트롤러 제어 명령에 해당하는 BCD에 관한 이야기를…

* 관련 글 : 일본 내수용 SONY ST-V5 튜너와 디지털 제어 시스템 (7)