글쓴이 : SOONDORI

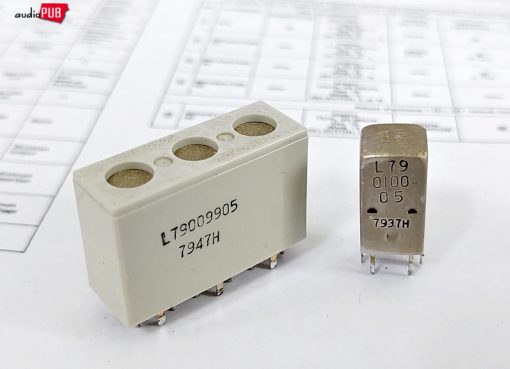

소스-게이트-드레인 층이 결합되는 FET 소자에서, 다음과 같이 적층 방식을 달리 한 경우.

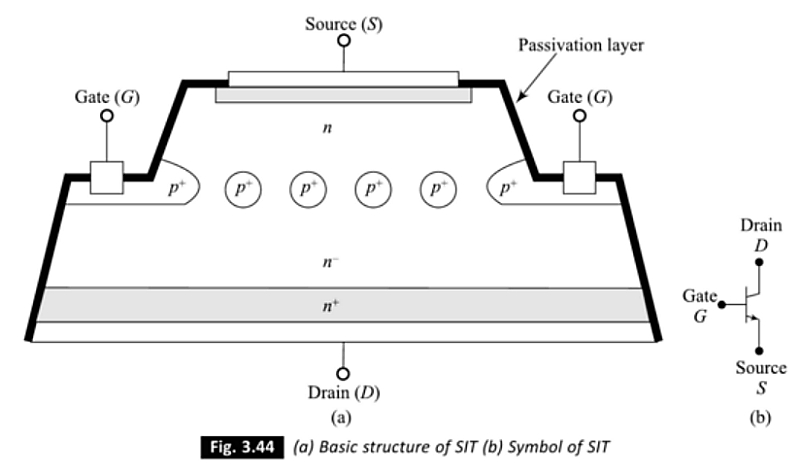

“… 3.20 정전 유도 트랜지스터(SIT) | 정전 유도 트랜지스터(SIT)는 고전력 고주파 반도체 소자입니다. 이 소자는 1987년 일본의 J. Nishizawa에 의해 개발되었습니다. SIT의 기본 구조는 그림 3.44(a)에 나와 있습니다. SIT는 3극 진공관의 고체 버전입니다. 이것은 p+ 게이트를 가진 n형 반도체 소자입니다. 그림 3.44(a)는 짧은 n형 다중 채널을 가진 수직 구조를 보여주며, SIT의 기호는 그림 3.44(b)에 나와 있습니다.

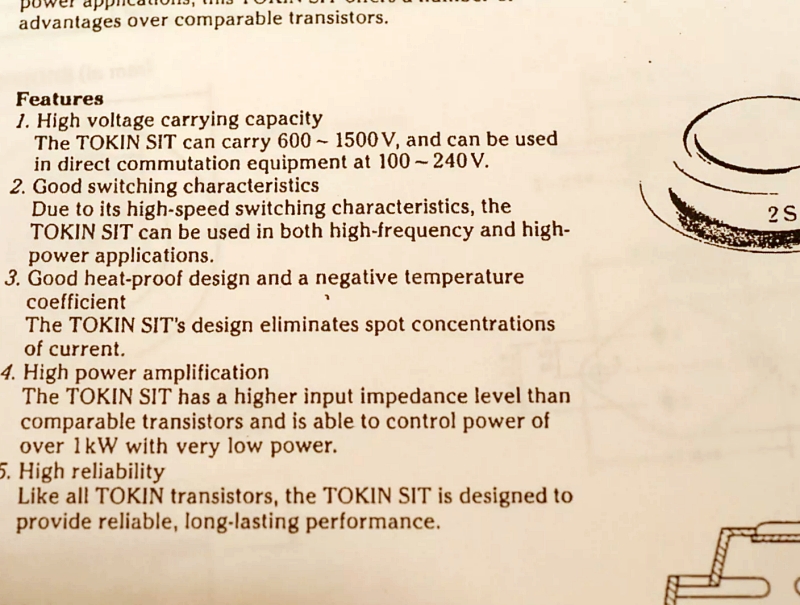

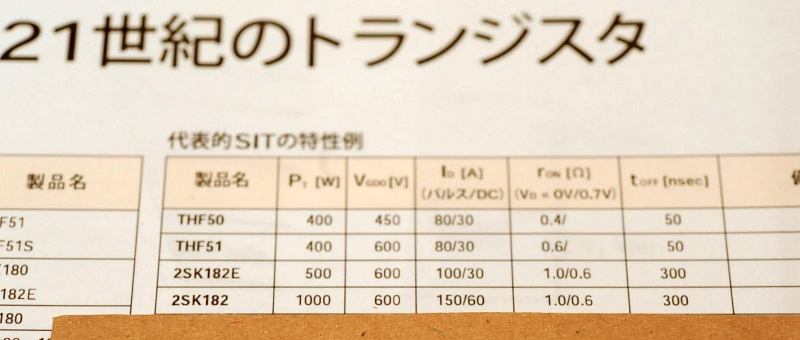

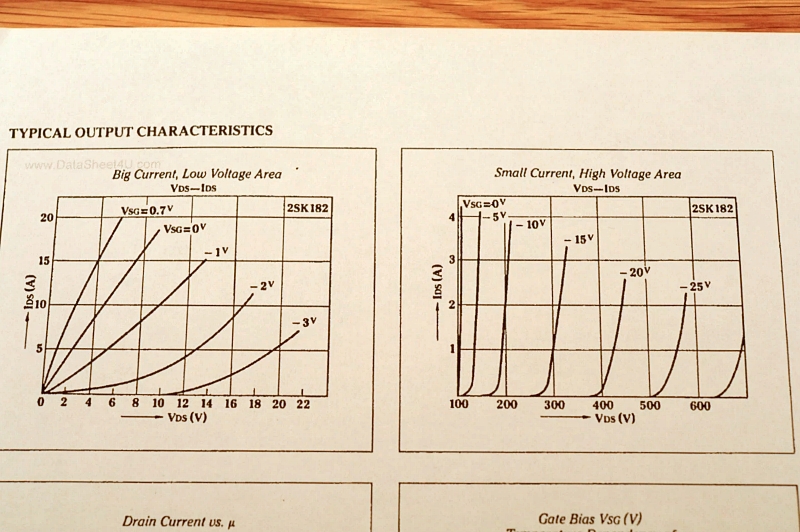

p+ 게이트는 그림 3.44(a)와 같이 네피택셜층에 매립되어 있습니다. p+ 매립 게이트 구조는 게이트와 소스 사이의 낮은 저항, 게이트와 소스 사이의 낮은 커패시턴스, 그리고 낮은 열 저항을 제공합니다. 낮은 채널 저항으로 인해 전압 강하가 적습니다. SIT는 높은 오디오 주파수 전력 처리 능력, 낮은 왜곡 및 적은 잡음을 가지고 있습니다 SIT의 켜짐 및 꺼짐 시간(ton 및 toff)은 매우 짧으며, 이 시간은 약 0.25µs ~ 0.35µs입니다. SIT의 작동 주파수는 약 100kHz입니다. SIT의 최대 전압 및 전류 정격은 각각 1200V와 300A입니다. 일반적으로 이 소자는 VGs가 0이고 VDs가 있을 때 켜짐 상태로 작동합니다. 다수 캐리어, 즉 전자는 소스 단자에서 n형 영역으로 흐르고 n형 채널을 통해 n 영역으로 이동한 후 마지막으로 nt 영역에 도달합니다. 드레인 전류 I는 드레인에서 소스로 흐를 수 있습니다…”

차곡차곡 위로 쌓는다… 줄임말로, Vertical의 V-FET. 수직 적재가 특이하다면, 수평 적재는 일반적이라는 뜻.

(표제부 사진 포함 출처 : https://www.ebay.ca/)

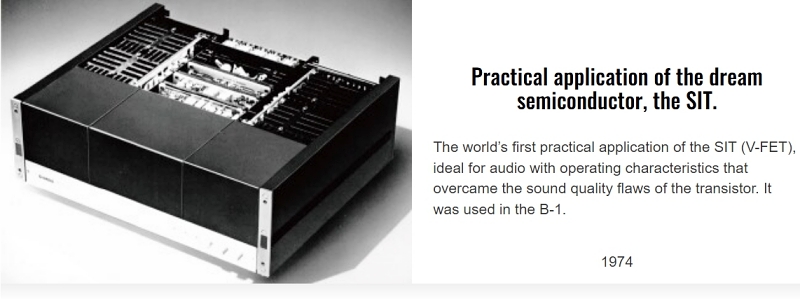

야마하가 공식 홈페이지에서 자랑하기를… 1974년의 B-1 파워앰프에서 그런 소자를 처음 사용하였다고.

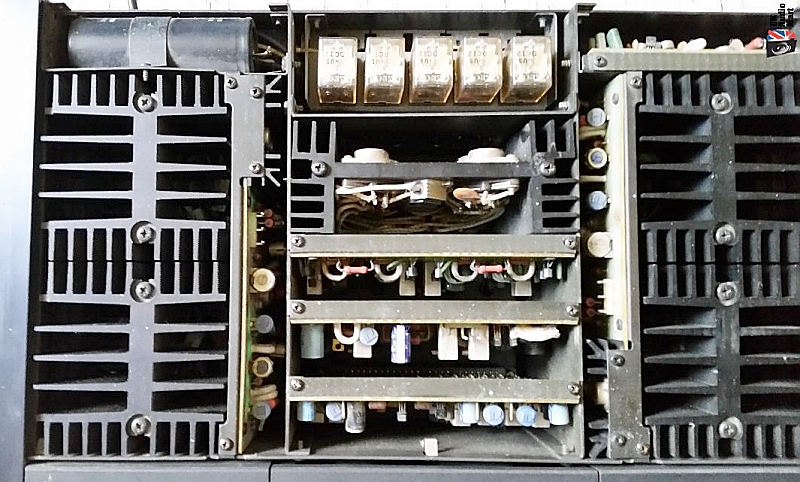

“겉으로 봐서 뭘 알곘노?” 뭐… 그랬나 보다.

* 관련 글 : 전혀 얇지 않은 Thick Film IC

![[과학기술사의 전자제작집 2권] 전자수면기와 시그널 트레이서 등](https://audiopub.co.kr/wp-content/uploads/2024/12/T_DIYer-Electronics-Magazine-B-0-510x369.jpg)